# **Modelling of Systems on Chip**

Part of Tutorial A: Automatically Realising Embedded Systems From High-Level Functional Models

Wido Kruijtzer, Victor Reyes NXP Semiconductors March 10, 2008

## **Outline**

- NXP Products / challenges

- Abstraction Levels

- Functional Modeling

- ▶ Architecture Modeling

- Summary

DATE 2008 Tutorial A - Wido Kruijtzer / Victor Reyes

## **NXP Semiconductors – Reborn and Renewed**

- Spin-out of Royal Philips Electronics' Semiconductor Division

- ▶ #2 in Europe, Top-10 global supplier

- ▶ Sales of €4.6 billion in 2007

- ▶ 37,000 employees / 7,500 engineers

- Investing €950 million in R&D annually

- ▶ 25,000+ patents

- ▶ More than 26 R&D centers in 12 countries

- ▶ Headquarters: Eindhoven, The Netherlands

- ▶ Key focus areas:

- Mobile & Personal, Home,

Automotive & Identification, Multimarket

NXP

DATE 2008 Tutorial A - Wido Kruijtzer / Victor Reyes

March 10,2008

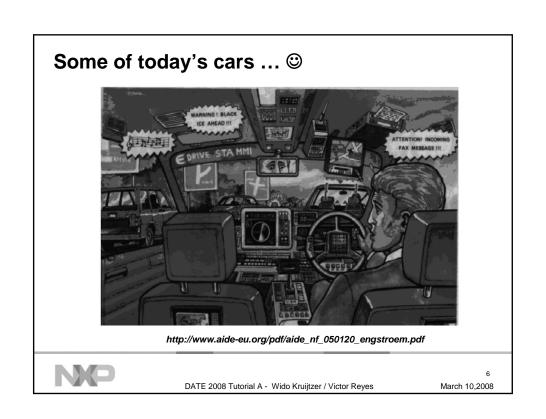

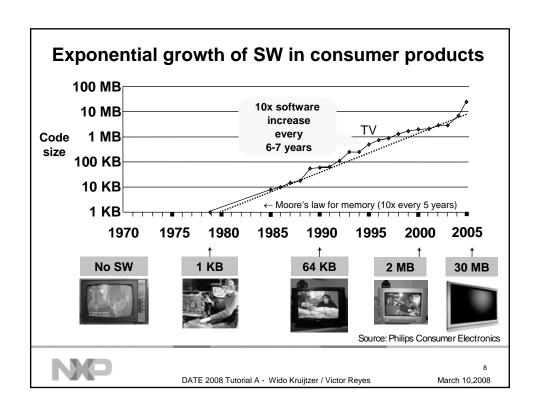

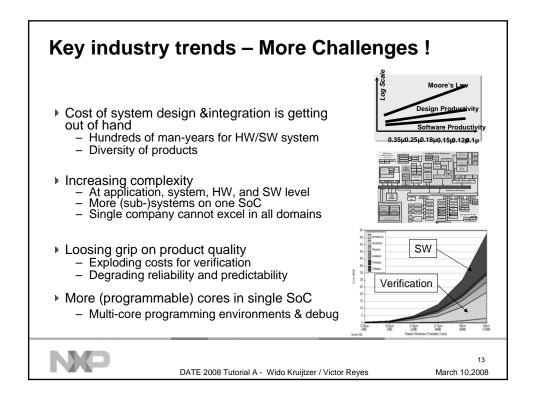

# Feature explosion in consumer products

Imaging Main display USB ▶ Wired Aux display Storage Removable Flash Camera SanDisk 🗷 Small HDD 3D display fixed flash 3D rendering SW features **Setup & Control** Audio audio codecs Instant messaging ring tones **PDA** MP3 Java Wireless GSM / GPRS modem 2-D game UMTS/3G Video Mpeg2 Bluetooth FM tuner Mpeg4 USB H264 **GPS** DivX RF-ID WLAN **DVB** tuner

DATE 2008 Tutorial A - Wido Kruijtzer / Victor Reyes

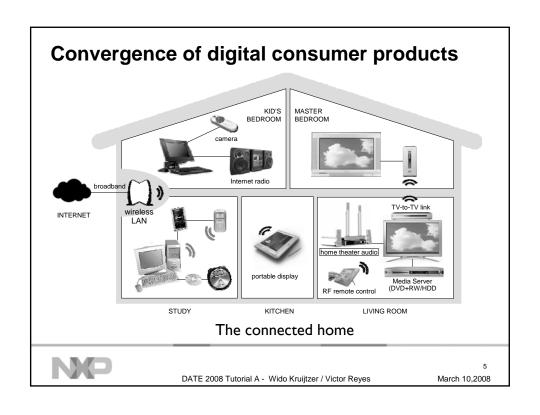

# **Convergence of digital consumer products**

#### Consequences:

- Large number of use cases

- ▶ Increasingly complex use cases

- Fast changing use cases with new applications appearing

- ▶ Format updates at a much higher rate than the device replacement rate

- Uncertain and diversified markets

- Late / changing product specs, short product life cycles

- Different customers / tiers have different requirements

- Move from implementations in hardware to software to cope with the variation and changes

#### **Consumer electronics**

#### **Characteristics**

- ▶ Cost pressure (< \$100 for electronics of large TV)</p>

- ▶ Low power consumption (no fan / mobile)

- ▶ Large series (> 0.5 million pieces)

- Robustness (no hazards, no reboots)

- Both control and signal processing

- ▶ Real-time constraints (no loss of data, guaranteed response)

- Increasing requirements for computation & communication (more functions, higher resolutions)

DATE 2008 Tutorial A - Wido Kruijtzer / Victor Reyes

March 10,2008

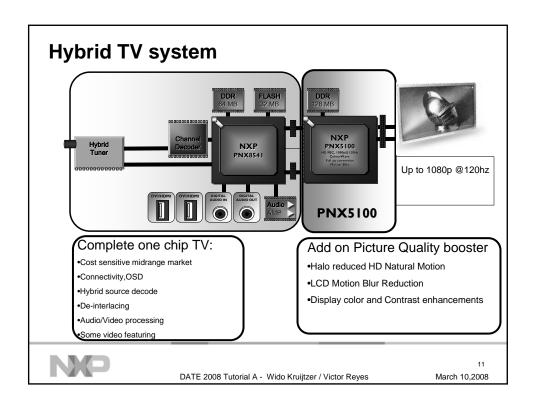

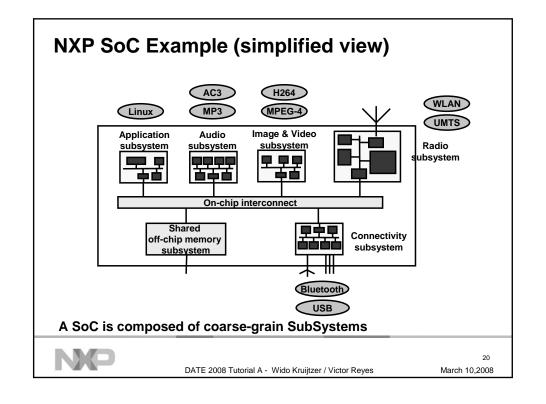

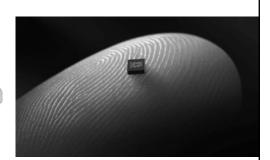

#### **Consumer domain demands SoC solutions**

- ▶ Highly integrated Systems-on-Chip to satisfy constraints on

- Cost

- Power consumption

- Form factor

- Ease of system integration

- Enabled by large volumes

- To amortize high NRE of SoC development

- Need to target sufficiently large market

- Optimized implementations with scarce resources

- Memory, bandwidth, compute cycles

DA

# **Design Solutions**

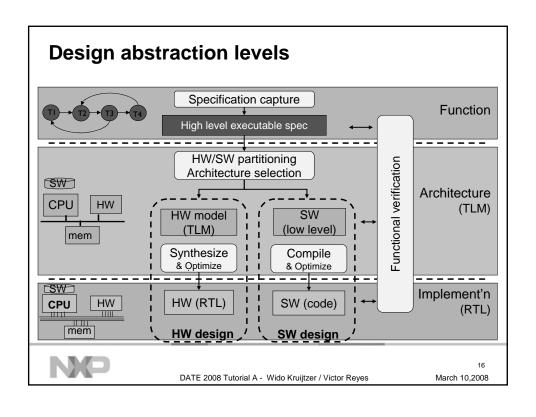

## NXP requires a design process that is

- Predictable in time and performance

- Efficient and high quality

#### The key elements of such a design process are

- Raising the level of abstraction

- System Level Design, System Integration and Verification

- ▶ High level of re-use

- IP reuse (HW, SW)

- Verification reuse

- Architecture reuse (HW,SW, appl.tasks) → Nexperia platforms

- Integrated design environments

- Automation of design flow → Builder tools

DATE 2008 Tutorial A - Wido Kruijtzer / Victor Reyes

March 10,2008

#### **Outline**

- NXP Products / challenges

- Abstraction Levels

- Functional Modeling

- Architecture Modeling

- Summary

15

DATE 2008 Tutorial A - Wido Kruijtzer / Victor Reyes

#### **SoC Level Functional Model**

Why do we need a functional model?

- ▶ Functional verification of algorithm

- Single model for HW and SW parts.

- ▶ Explore algorithmic tradeoffs

- ▶ Estimate resource requirements

- Computational load, Communication load

DATE 2008 Tutorial A - Wido Kruijtzer / Victor Reyes

March 10,2008

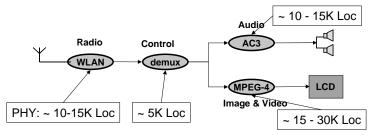

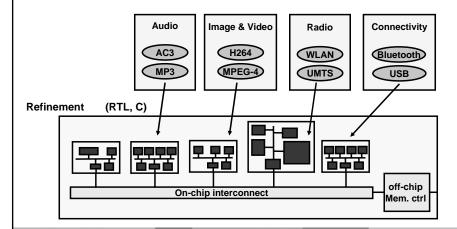

# **SoC Level Functional Model (toplevel)**

Difficult to create an executable SoC level functional model

- Each sub-function contains hundreds of sub-blocks

- Functional decomposition, Interfaces

- Characteristic per functional sub-system differ

- Different semantics needed

- Dataflow, Process networks, Discrete Event, State Machines

- Different algorithmic tradeoffs

22

DATE 2008 Tutorial A - Wido Kruijtzer / Victor Reyes

- Different Models of Computation (semantics)

- ▶ Single functional model too complex to handle by single designer

- ▶ Limited tool support

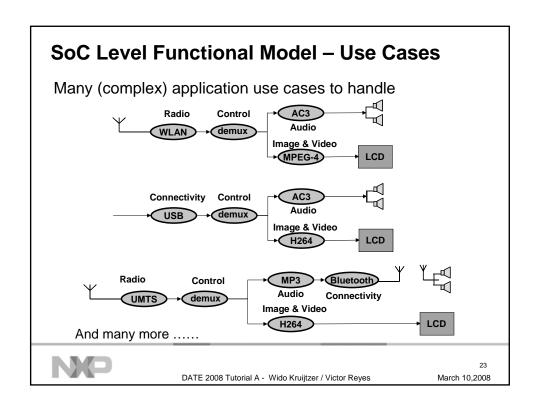

- Many application use case to cover

- "All in one" functional model not preferred

- ▶ IP Re-use, platform based design

- Many design teams involved

- Multi site, Multi culture

Solution: Divide & Conquer approach

NXP

DATE 2008 Tutorial A - Wido Kruijtzer / Victor Reyes

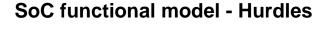

# Functional Modeling at IP / Sub-System Level

Benefits of multiple functional models:

- Complexity can be handled more easily

- Optimized tools available for implementations

- Specific implementation technology

- Domain specific, single semantics

- Specialized domain know-how (e.g. competence centre)

- ▶ Different life-cycles → re-use

NXP

DATE 2008 Tutorial A - Wido Kruijtzer / Victor Reyes

25 March 10,2008

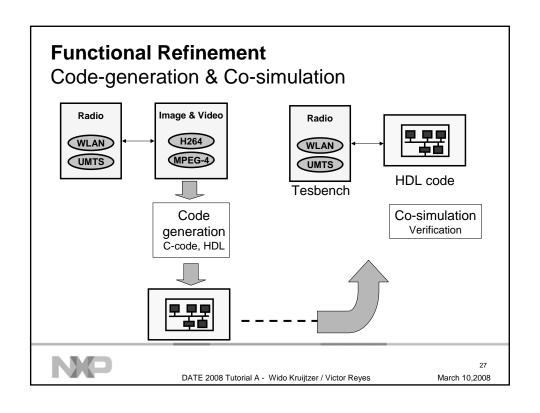

# **Functional Model Refinement**

▶ Functional refinement directly to implementation level

NXP

DATE 2008 Tutorial A - Wido Kruijtzer / Victor Reyes

# Functional modeling - Simulink

### Bluetooth - EDR

- Started with Simulink built-in models.

- Developed a complete TX chain, including analog/RF blocks.

- Simulated the transfer function of the modulator and verified it against the Bluetooth standard specification

- Converted the design into fixed-point format.

- Verified the functionality of the fixed-point design against the Bluetooth standard.

- Generated (manually) a bit-compatible RTL description of the Simulink fixed-point model.

- Evaluated the modulator on an FPGA platform.

Next step: HDL generation directly from Simulink

30

DATE 2008 Tutorial A - Wido Kruijtzer / Victor Reyes

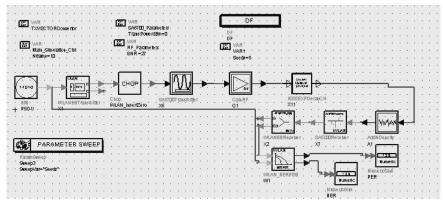

# Functional modeling - ADS/Ptolemy

Wireless LAN radio system

▶ Functional model used as testbench for circuit design

DATE 2008 Tutorial A - Wido Kruijtzer / Victor Reyes

March 10,2008

## What's next after functional modeling?

Functional to implementation problems

- ▶ SoC integration happens at RTL / C level

- Complex and error prone

- Iterations are not possible (first implementation/configuration that work instead of best/optimized one)

- ▶ Main usage of the Implementation level is for pre-silicon verification

- But complete system is hard to simulate/verified all together

- ▶ SoC integration at the implementation level introduces a big gap

- Complex and error prone

Iterations are not possible (first implementation that work instead of best one)

An intermediate step before implementation is required

- → Architecture level

- Main usage is SoC integration, analysis and debug

DATE 2008 Tutorial A - Wido Kruijtzer / Victor Reyes

## **Outline**

- NXP Products / challenges

- ▶ Abstraction Levels

- Functional Modeling

- ► Architecture Modeling

- Research challenges

- ▶ Conclusions

DATE 2008 Tutorial A - Wido Kruijtzer / Victor Reyes

33

March 10,2008

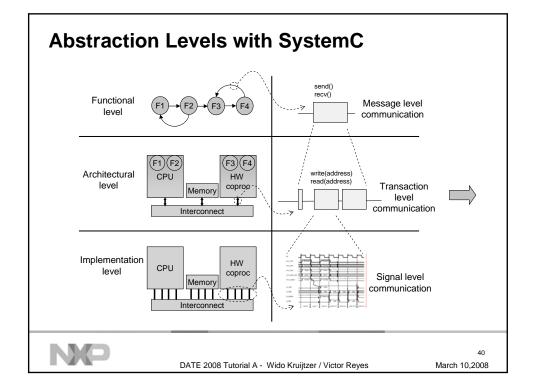

# **Architectural Level – Key concepts**

- Abstraction

- Increasing block granularity

- Gates (80's), HDL (90's), IP blocks (2000), SubSystems (2010)

- From RTL to TLM (Transaction Level Modeling)

- but TLM covers only HW architecture, all system aspects need to be modeled together (i.e. architecture, application, constraints, etc)

- ▶ Separation of concerns

- Computation / Communication / Cost

- Behavior / interfaces

- ▶ Refinement

- Synthesis and transformation techniques

- Standards

- OSCI (SystemC and TLM standards)

- SPIRIT (IP-XACT)

DATE 2008 Tutorial A - Wido Kruijtzer / Victor Reyes

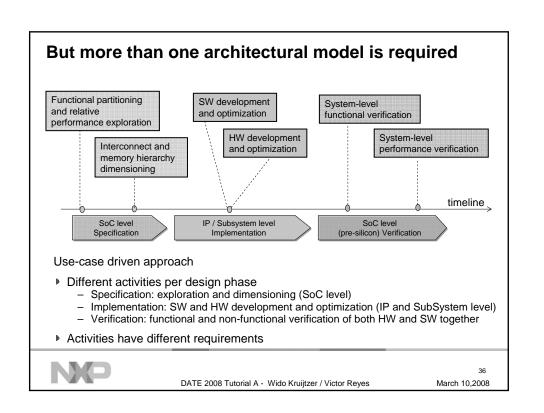

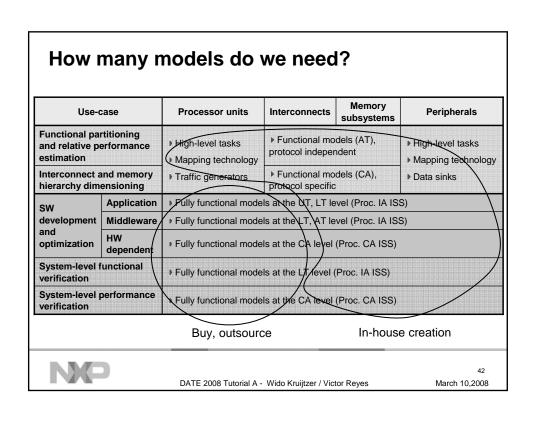

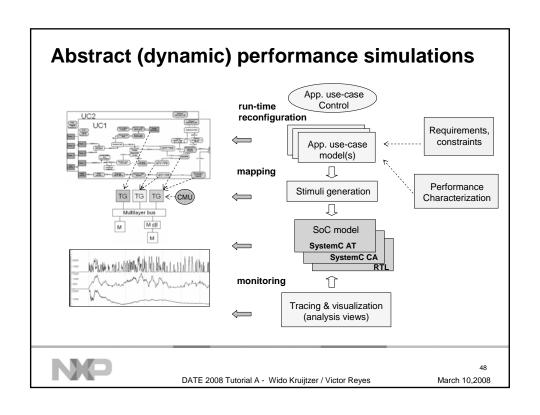

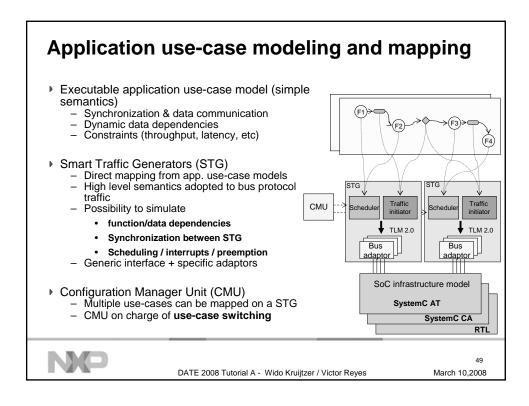

# Different use-cases, different requirements

| Use-case                                                    |                 | Description                                                                                                                                             | RTL<br>speed<br>up | Behavior<br>accuracy                             | Timing accuracy        |

|-------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------------------------|------------------------|

| Functional partitioning and relative performance estimation |                 | Enable extensive architectural exploration (what-if scenarios)     Focus on: task mapping, task scheduling, memory allocation, resource allocation, etc | x10⁴               | Mixed abstract performance and functional models | Relative<br>(fidelity) |

| Interconnect and memory hierarchy dimensioning              |                 | ► HW architecture dimensioning Focus on: bandwidth, latency, buffering, arbitration policies, etc                                                       | x10²               |                                                  | Absolute ±10%          |

| SW<br>development<br>and<br>optimization                    | Application     | ► End-user SW applications (platform services based)  ► Multicore debugging                                                                             | x10 <sup>4</sup>   | Fully<br>functional<br>models                    | Absolute<br>±20%       |

|                                                             | Middleware      | ► Complex algorithms and codecs (H264, MP3, UMTS, AES etc) ► SW platform services                                                                       | x10 <sup>3</sup>   |                                                  | Absolute ±10%          |

|                                                             | HW<br>dependent | ► Low-level drivers, HW abstraction layers (HAL)  ► Must be very optimized                                                                              | x10 <sup>2</sup>   |                                                  | Absolute ±1%           |

| HW development and optimization                             |                 | ► VP as a system-level test-bench for the HW IP  ► High Level Synthesis / RTL co-simulation (transactors)                                               | x10 <sup>3</sup>   |                                                  | Absolute ±10%          |

| System-level functional verification                        |                 | ► HW/SW integration and verification (complete SW stack)  ► Extensive verification of scenarios                                                         | x10 <sup>3</sup>   | Fully<br>functional<br>models                    | Absolute ±10%          |

| System-level performance verification                       |                 | ► Very accurate performance and power estimations  ► Representative (worst-case) scenarios                                                              | x10 <sup>2</sup>   |                                                  | Absolute ±1%           |

DATE 2008 Tutorial A - Wido Kruijtzer / Victor Reyes

37

March 10,2008

## Different requirements, different models?

- In an ideal world one model fits all

- Ultra fast models + 100% cycle accurate + push-button availability

- Unfortunately today we still need the right model for the right use-case...

but one model per use-case is an overkill

- Huge effort to create and maintain every model

- How to assure consistency between models?

- ▶ Model reuse and refinement is a must...

but modeling is a multidimensional problem

- High speed models contains very little time information

- Very accurate models are typically slow and are difficult to create

- No clear refinement paths from one model to another

- And different types of models have different particularities

- Processing units (CPU, DSP, etc)

- Interconnects (busses, bridges, routers, etc)

- Memory subsystem (L1-L2 cache, memory controllers, memories, etc)

- Peripherals (IO blocks and slave HW accelerators)

Getting to the right model is the critical task

38

March 10,2008

DATE 2008 Tutorial A - Wido Kruijtzer / Victor Reyes

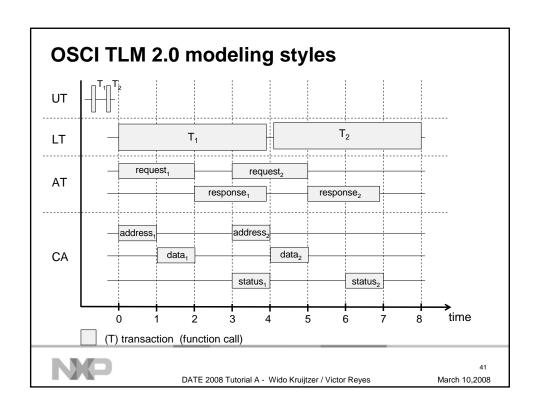

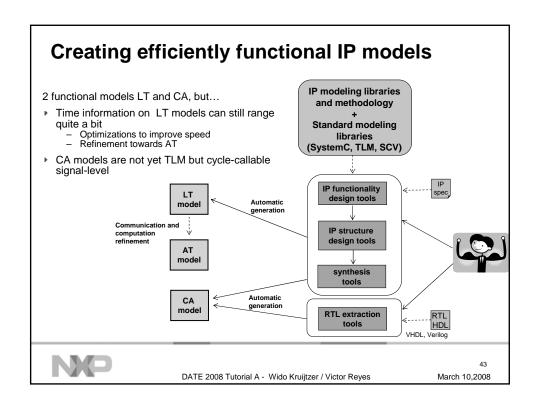

# **Modeling concepts**

- Minimizing the modeling effort

- Library of predefined building blocks to compose IP models

- Well defined methodologies and guidelines

- Standard set of IP interfaces to assemble IP models (avoid adaptors)

#### Modeling for speed

- Minimize the number of simulation events / context switches

- Coarse grain computation and communication

- Binary translation techniques for processors / host-code emulation techniques

#### Modeling timing

- Accurate timed models are very hard to create

- Approximated timed models are easier (but when it is good enough?)

- Define accuracy windows, where the window size depends on the use-case

- Behavior/Computation refinement

- Cost (timing) refinement

Still ad-hoc, proprietary solutions

[TLM]

NXP

DATE 2008 Tutorial A - Wido Kruijtzer / Victor Reyes

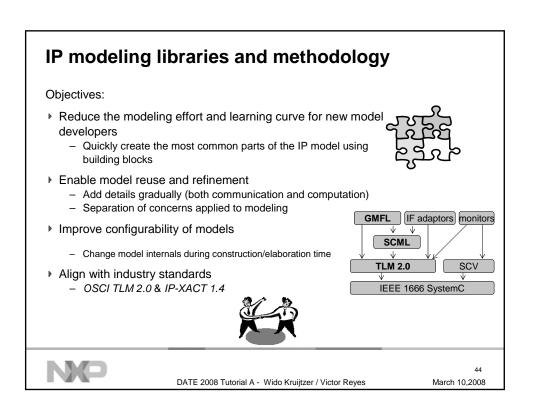

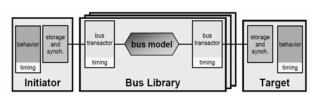

- Methodology for model re-use

- Use-case determine for bus model

- Re-use peripheral model for multiple use-cases

- Separation of behavior, communication and timing

- Focus on communication refinement

- generic interfaces + specific adaptors

- ▶ Simple modeling pattern supported by a library of predefined blocks

- SystemC Modeling Library (SCML) http://www.coware.com/solutions/tlm.php

DATE 2008 Tutorial A - Wido Kruijtzer / Victor Reyes

March 10,2008

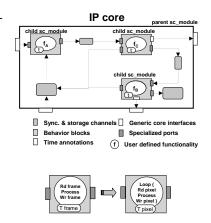

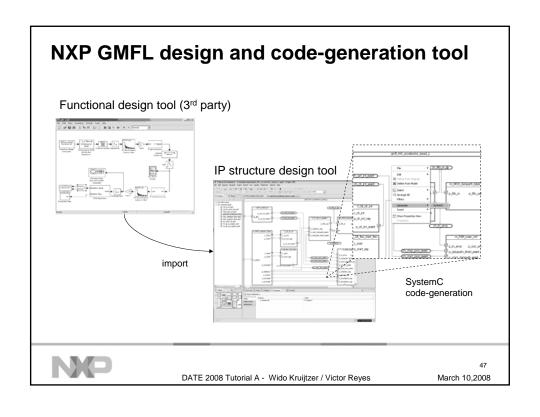

#### **NXP GMFL**

Generic Modeling Features Library

- Library of predefined blocks built on top of SCML

- Extend and complement SCML capabilities

- More methodology and guidelines

- Focus on behavior modeling and refinement

Explicit synchronization, data and control flow

#### Key concepts are:

- Hierarchical modeling

Structured, reusable code

Closer to HW designers

- Dynamic layout

- Add/remove functionality during elaboration

- Block refinement

- Design and code-generation tool

DATE 2008 Tutorial A - Wido Kruijtzer / Victor Reyes

### **Summary**

- SoC design challenges require moving up in the abstraction level and exploit reuse at all levels

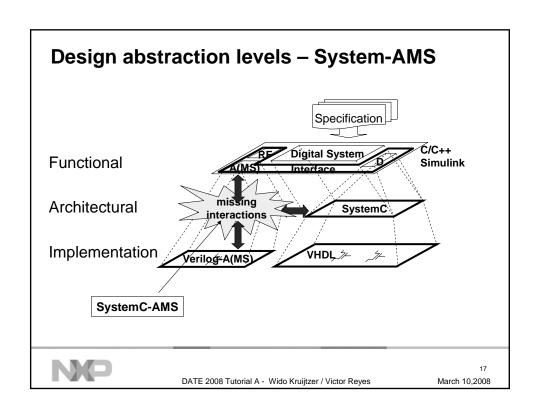

- Abstraction levels

- Multiple domains (digital, analogue, RF)

- Multiple languages (UML, C++, Simulink, SystemC, VHDL, Verilog-AMS, etc)

- ▶ Functional modeling → divide & conquer

- Domain specific functions, different semantics, different algorithmic trade-offs

Multiple functional use-cases

- Most tools provide a path to implementation

- ▶ An integration level above implementation is required → Architectural Level

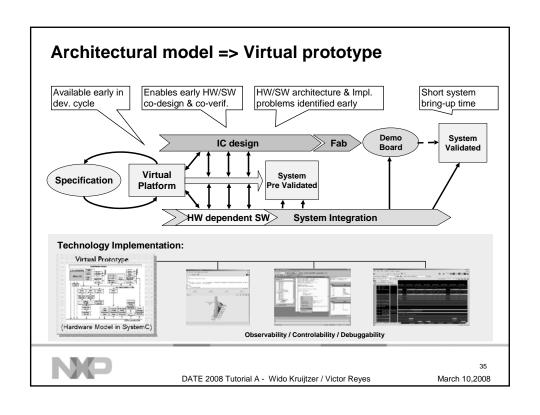

- Architecture model => Virtual prototype

- Different architectural use-cases with different requirements => the right model for the right use-case

- Getting to the models is still the critical task => how to tackle this

- · IP Modeling methodologies and libraries

- · Automatic generation from different tools

DATE 2008 Tutorial A - Wido Kruijtzer / Victor Reyes

March 10,2008

### References

- [DAC2000] E.A. de Kock, G. Essink, W.J.M. Smits, P. van der Wolf, J-Y. Brunel, W.M. Kruijtzer, P. Lieverse, K.A. Vissers; "YAPI: Application Modeling for Signal Processing Systems "in Proceedings of the 37th Design Automation Conference, Los Angeles, 2000

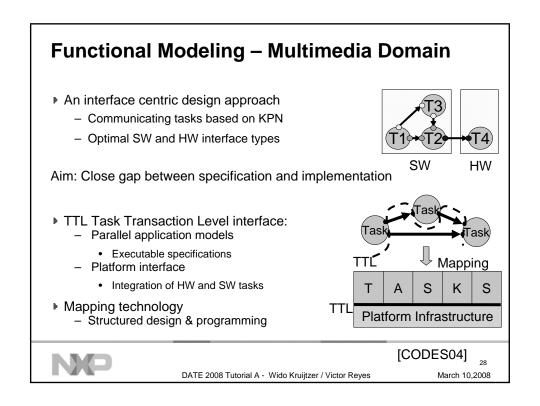

- [CODES04] Pieter van der Wolf, Erwin de Kock, Tomas Henriksson, Wido Kruijtzer, Gerben Essink, "Design and Programming of Embedded Multiprocessors: An Interface-Centric Approach", Int. Conf. on Hardware/Software co-design and System synthesis, September 2004

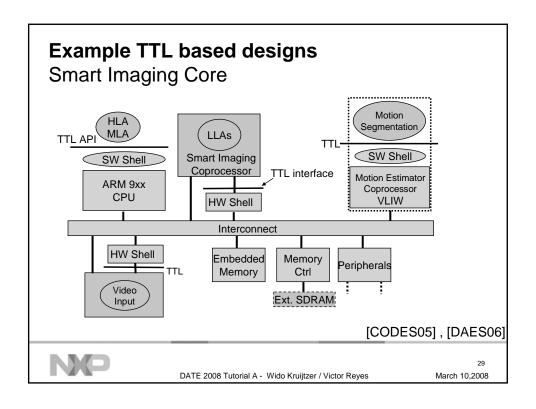

- [CODES05] Wido Kruijtzer, Winfried Gehrke, Victor Reyes, Ghiath Alkadi, Thomas Hinz, Jörn Jachalsky, Bruno Steux; "The Design of a Smart Imaging Core for Automotive and Consumer Applications: A Case Study" in Int. Conf. on Hardware/Software co-design and System synthesis, September 2005

- [DAES06] Wido Kruijtzer, Victor Reyes, Winfried Gehrke; "Design, Synthesis and Verification of a Smart Imaging Core using SystemC" in Design Automation for Embedded Systems, An International Journal from Springer, Volume 10, Numbers 2-3, September 2006, pp. 127-155(29). Special Issue on SystemC-based System Modeling, Verification and Synthesis. DAC07: Slider

- [DAC2007] Walter Tibboel, Victor Reyes, Martin Klompstra, Dennis Alders; "System-Level Design Flow Based on a Functional Reference for HW and SW" in Proceedings of the 44th Design Automation Conference, San Diego, 2007

- [SCML] http://www.coware.com/solutions/scml\_kit.php

- [TLM] http://www.systemc.org/downloads/standards/

- [ESL book] Brian Bailey, Grant Martin, Andrew Piziali, "ESL Design and Verification: A Prescription for Electronic System Level Methodology" The Morgan Kaufmann Series in Systems on Silicon

52

DATE 2008 Tutorial A - Wido Kruijtzer / Victor Reyes